- FPGA可重復配置和測試系統

- 系統軟硬件交互流程

- 配置速度測試實驗

從制造的角度來講,FPGA測試是指對FPGA器件內部的邏輯塊、可編程互聯線、輸入輸出塊等資源的檢測。完整的FPGA測試包括兩步,一是配置FPGA、然后是測試FPGA,配置FPGA是指將FPGA通過將配置數據下載編程使其內部的待測資源連接成一定的結構,在盡可能少的配置次數下保證FPGA內部資源的測試覆蓋率,配置數據稱為TC,配置FPGA的這部分時間在整個測試流程占很大比例;測試FPGA則是指對待測FPGA施加設計好的測試激勵并回收激勵,測試激勵稱為TS。

通常來說,要完成FPGA內部資源的完整測試需要針對不同的待測資源設計多種配置圖形,多次下載到FPGA,反復施加激勵和回收測試響應,通過對響應數據的分析來診斷故障。因此,用于FPGA測試的儀器或系統的關鍵技術在于:如何加快單次配置的時間,以節省測試過程中的配置時間開銷;如何實現自動重復配置和測試,將FPGA較快速度的在線配置和快速測試結合起來。

由于一般的集成電路自動測試儀ATE為通用IC測試設計,但FPGA測試有上述特殊性,在芯片功能測試之前必須對其進行特定的配置,否則芯片是不具備內部電路結構的,內部資源將無法測試,而通用的ATE要完成測試步驟中的配置功能時,需要以人工或通過電腦專門編程修改配置數據生成測試系統可執行的測試激勵形式進行配置,且如果配置數據較多,這個轉換過程將可能比較復雜,易用性不強,無法高效地用于FPGA器件的測試中,需要對FPGA測試設計專用的測試平臺以滿足其配置測試需求。

我們設計的系統實現了快速重復配置和測試的功能,配置數據可以直接引用EDA軟件生成的位流文件而不需要像ATE一樣轉換成繁雜的測試激勵形式,相較于ATE有一定的優勢,對FPGA測試有一定的使用價值。

FPGA可重復配置和測試系統結構概述

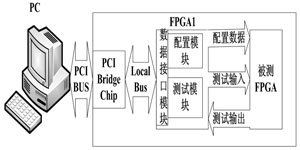

系統框圖如圖1所示。

圖1可重復配置測試系統結構框圖

系統功能的實現包括軟件和硬件兩部分。硬件部分包含PCI橋接芯片、FPGA1中的數據接口模塊、配置模塊、測試模塊和被測FPGA。軟件部分包含對實現FPGA配置部分的代碼和實現FPGA測試部分的代碼。FPGA1中的各硬件模塊通過EDA軟件以JTAG接口固化FPGA1中,其中FPGA1中的配置模塊負責接收來自PC方軟件發送的配置數據,并產生對被測FPGA的配置時序,完成配置步驟,測試模塊負責發送測試激勵和回收被測FPGA的響應數據,等待PC方軟件的回收。

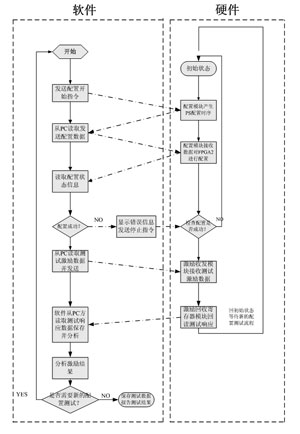

系統軟硬件交互流程

整個系統通過軟硬件的數據交互實現對被測FPGA的自動配置和測試的流程,軟硬件交互的流程從圖2可以體現:系統啟動后,首先需要開始對被測FPGA進行數據配置,由軟件向硬件發送配置開始指令,硬件接收指令后對被測FPGA產生配置開始的時序,告訴被測FPGA準備接收配置數據。當軟件查詢到配置模塊中的狀態寄存器值代表等待數據時開始發送配置數據。配置數據發送完成后,軟件通過讀取配置模塊的狀態寄存器值判斷配置是否成功,決定是否可以開始測試。如果配置成功,軟件則開始向被測FPGA發送測試激勵數據并讀回測試響應保存在電腦中,由軟件對測試響應進行分析決定是否需要進行下一次配置和測試流程。如果需要,在一定的延時之后軟硬件將回復初始狀態,并選擇新的配置數據和測試數據,開始新一輪的配置后測試流程。[page]

圖2FPGA芯片自動重復下載自動測試系統軟硬件交互流程圖

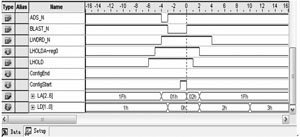

軟硬件數據交互的通路是PCI總線,軟件向FPGA1發送指令或數據時,軟件通過PCI應用編程接口函數將數據放到PCI總線上,PCI橋接芯片將較為復雜的PCI接口信號轉化為相對簡單的LocalBus數據信號,由FPGA1中的接口模塊接收并產生相應的動作。而軟件向FPGA1讀取數據的通路則相反。圖3和圖4分別是軟件在VC++6.0環境中斷點調試發送指令和軟件向FPGA1發送指令時由嵌入式邏輯分析儀SignalTAPII捕捉到的指令數據和接口模塊波形。

圖3VC++6.0環境中斷點調試指令發送

圖4嵌入式邏輯分析儀SignalTAPII波形

圖4中ADS_N、BLAST_N、LWORD_N、LHOLD、LHOLDA是LocalBus的接口信號,ConfigEnd和ConfigStart是分別代表配置結束和配置開始的標志寄存器,LA是接口的地址信號,用于模塊中控制寄存器的尋址,LD是接口的數據信號,用于指令數據的發送和數據的回收。

以配置開始指令的發送為例,從圖3圖4兩圖中可以看出軟硬件交互過程中的指令發送方式,在VC++中單步調試,發送一個開始指令0x01到配置命令寄存器地址0x01,通過硬件模塊的接口動作,用嵌入式存儲器SignalTapII中捕捉到LA的數據為1h,LD上的數據為1h后ConfigStart寄存器置高,配置開始。

配置速度測試實驗

軟硬件具體方案設計完畢后,軟件在VisualC++6.0環境下實現并調試。硬件在QuartusII7.1軟件下編譯。

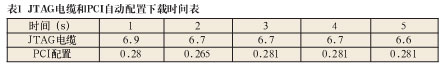

為了對比基于PCI總線的FPGA高速配置方案與基于ByteBlasterIIJTAG下載電纜的速度性能,首先使用QuartusII7.1軟件采用JTAG方式對FPGA2配置5次,計算每次下載所示時間,得到如表1中所示的數據;再使用本系統中基于PCI總線的配置功能對FPGA2配置5次,軟件會自行計算總的下載時間,得到如表1中所示的數據:

從表1的數據對比中可以看到,基于PCI總線的自動下載配置方式要比基于JTAG電纜的下載配置方式提高超過20倍的速度,如果使用基于JTAG電纜對某大容量的FPGA下載需要近20分鐘的話,使用PCI下載方式則只需不到1分鐘的下載時間,具有明顯的速度優勢,大大節省了FPGA測試中的數據配置時間。

測試總結

該FPGA芯片測試平臺具有以下特點:

(1)針對FPGA測試的特點:需要重復對待測FPGA配置,設計了FPGA在線配置模塊和自動測試模塊,從概念上初步實現了自動重復下載和重復測試的功能,為FPGA自動化測試尋找到一個好方法;

(2)利用軟件的靈活性提高了測試系統中具有可觀察性好和可控制性強的優勢;利用硬件結構上并行度高、速度快的優勢提高了測試的效率;

(3)相較于專業的ATE設備,該系統軟件可控性更強,配置數據更方便。