調(diào)試數(shù)字硬件設(shè)計可能壓力大、耗時長,但我們有辦法來緩解壓力。

工程設(shè)計項目中最令人振奮的時刻之一就是第一次將硬件移到實驗室準備開始集成測試的時候。開發(fā)過程中的這個階段通常需要很長時間,也會對所有的項目工程師造成很大的壓力。不過,現(xiàn)有的工具和方法能減輕壓力,幫助推進項目進展。

讓我們來看一下,如何在將設(shè)計推進到更高層面的過程中最大限度地減少可能發(fā)生的任何問題,以及如何快速順利地通過調(diào)試階段。

從第一天起就要設(shè)想如何進行測試?

所有工程師都知道,隨著開發(fā)進程的推進,修改問題的成本也會相應增加。一旦設(shè)計方案最終定型并投產(chǎn),再修改引腳輸出錯誤的成本必然高于早期設(shè)計評估時修改的成本。此外,在測試與集成方面也同樣存在成本問題,越早考慮硬件、FPGA、系統(tǒng)等的測試問題并編寫測試規(guī)范,就越便于工程設(shè)計團隊考慮到必要的測試點、連接和功能性。測試的目的是確保能推出可滿足用戶具體要求的安全系統(tǒng)。因此,我們必須確保測試能體現(xiàn)所有要求,而功能測試則要求應能實現(xiàn)流程傳遞并可跟蹤設(shè)計要求(即每個測試均應滿足其所對應的需求)。

此外,對設(shè)計驗證模型進行編輯也是一種非常好的做法,能詳細說明測試每項功能要求的方法,如具體的測試、分析或讀取方法(條件是在另一個項目上較早明確或測試了相關(guān)要求)。文檔(圖1)可能還涉及哪些測試需用于設(shè)計驗證,以及哪些用于生產(chǎn)運行。在項目階段早期即完成上述文檔,可確保系統(tǒng)設(shè)計團隊和測試設(shè)備的設(shè)計團隊獲得明確的基本方法。

但是,在進行功能性測試之前,設(shè)計工程師還必須確保底層硬件的正確性。他們通常需要包含電源、性能和硬件基本驗證等內(nèi)容的硬件級測試規(guī)范,而硬件基本驗證需在功能測試之前進行。

明確需要何種測試設(shè)備以及什么樣的性能非常重要,例如需要分析信號發(fā)生器和邏輯分析器是否能提供足夠的存儲深度和工作頻率?此外,還需明確是否需要更專業(yè)化的測試設(shè)備,如任意波形生成器、高穩(wěn)定性頻率參考等。

設(shè)計階段應包括的內(nèi)容

在硬件的設(shè)計過程中,或許應包括幾項設(shè)計特性和功能,以使電路板的測試能夠更方便。相關(guān)要求可能比較簡單,也可能較有深度。

最簡單也是最常見的測試規(guī)定是在所有電壓源上放置測試點,這避免了探詢焊接點時造成損壞的可能性。不過,還有一種比較好的辦法,是讓連接接地(0V)返回的焊盤靠近電壓測試點,從而簡化測試工作。若采用高值電阻來保護這個測試點,就能限制測試中意外短路情況下的電流。我們也可考慮給這些焊盤添加測試引腳,使其連接到可隨后在生產(chǎn)運行期間記錄結(jié)果的自動測試系統(tǒng)上。

此外,監(jiān)控時鐘和復位輸出的功能至關(guān)重要。因此,在復位線路上放置測試點不矢為一種好辦法。另外,還應確保正確端接不使用的時鐘緩沖器并添加測試點,從而便于對時鐘進行探詢。此外還可考慮添加測試端口,通過信號發(fā)生器、邏輯分析儀或其他測試工具來實現(xiàn)信號的注入和提取。

為了幫助原型設(shè)計達到功耗要求,如果可能,通常比較好的做法是在電壓調(diào)整器的輸出端串聯(lián)低值電阻(10毫歐、100毫歐等),以便精確測量電源軌上的電流。

眾多FPGA器件也都能提供采用溫度二極管監(jiān)控芯片溫度的方法。需要想辦法為二極管提供恒定電流。測定芯片溫度有助于我們確保結(jié)溫不超出額定值。要確保所有組件都適當就位,明確是否符合設(shè)計方案的要求,特別是如果只有一個上拉或下拉電阻應就位并選擇配置模式時更是如此。

檢查完印刷電路板上的各組件之后,下一步就是首次給電路板加電。對于任何工程師來說,這都是非常緊張的時刻。但是,在設(shè)計階段(測試點、電流感測電阻等)編制的測試規(guī)定將在這時發(fā)揮很大的協(xié)助作用。第一步是確保負載點和其他穩(wěn)壓器的功率輸出不發(fā)生短路返回。您可能會在帶載器件(具有高電流要求)的電源軌上發(fā)現(xiàn)低阻抗,不過阻抗應大于1歐姆。

對于業(yè)界率先實現(xiàn)的同類型設(shè)計(即新產(chǎn)品首次進行實際構(gòu)建)而言,我們或許應該制定更深入的設(shè)計決策,例如將電源與下游電子器件進行分離處理。這樣,我們就能確保電源和上電順序都能正常工作,從而避免下游組件的應力過大或損壞。更詳盡的前端設(shè)計階段有助于測試工作的例子還有一個,那就是確保JTAG端口除了在系統(tǒng)中對所有FPGA或處理器進行編程之外還能有更多用處,例如通過邊界掃描測試來進行初始的硬件驗證等。邊界掃描測試對在測試階段早期減少硬件設(shè)計風險非常有用,同時也要求對設(shè)計方案進行優(yōu)化,以確保最大限度地覆蓋邊界掃描器件。

[page]

明確硬件特性

系統(tǒng)第一次到達實驗室時,您要做的第一件事情就是確定硬件底層模塊是否適合做進一步的測試。相關(guān)檢查包括模塊的初步通電測試,這是個緊張的過程。剛拿到模塊,您希望確保其準確投產(chǎn),能夠成功實現(xiàn)首次通電啟動。第一步就是確保所有的組件都各就其位,引腳“1”正確定位,而且任何帶極性的組件都準確放置。設(shè)計中通常可能包含眾多無需檢查定位的組件,例如那些適合不同版本或不同構(gòu)建選項的組件。

如果您確定所有電源軌都沒有短路,那么下一步就該加電了。初次加電時,我傾向于采用分兩個階段進行的方案。第一個階段是采用低電壓(0.5V)和低電流,以確保不錯過信號層或電壓軌之間的任何短路情況;第二個階段是用正確的工作電壓在設(shè)定的電流限值內(nèi)加電,看看是否獲得預期電流(不要忘了突入電流問題)。

成功給設(shè)計方案加電后,下一步就是確定電源上電的排序、復位以及時鐘是否能按設(shè)想的工作。切記,要確保復位時長超過所有時鐘,并在釋放之前處于穩(wěn)定狀態(tài)。明確硬件特性的下一步就是確保能通過JTAG鏈看到硬件,這使我們不僅能對FPGA編程,而且還能執(zhí)行邊界掃描測試。邊界掃描測試能幫助我們快速測試器件之間的互連,通過測試存儲器可確保其正常工作,如開發(fā)回環(huán)接插件也可回轉(zhuǎn)輸入輸出。JTAG和邊界掃描測試可在進一步詳細的測試之前消除設(shè)計風險。

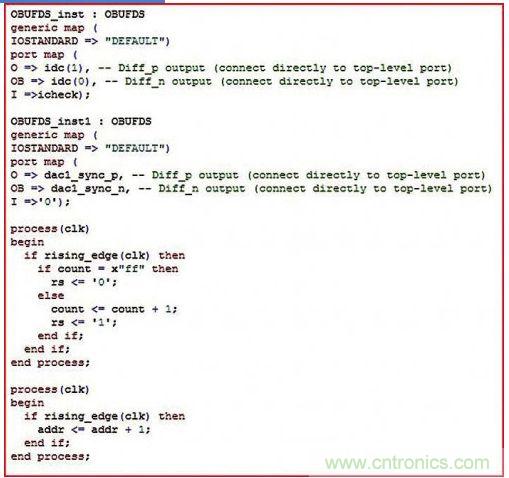

如果您的設(shè)計在硬件和FPGA層面上都很復雜,那么簡化版的RTL將有助于測試開發(fā)板以及FPGA和外設(shè)(圖2)之間的接口。對高速接口設(shè)計而言,更是如此。我們可結(jié)合采用優(yōu)化的RTL和賽靈思 ChipScope?工具來捕獲數(shù)據(jù),以及預載了數(shù)據(jù)模式的Block BRAM來發(fā)揮激勵作用。這種方法對采用ADC和DAC連接FPGA的情況尤其有用。在此情況下,您應發(fā)揮FPGA的可再編程特性來最大限度地進行設(shè)計開發(fā),實現(xiàn)ADC和DAC的參數(shù)測試,比如噪聲/功率比、無雜散動態(tài)范圍和有效比特位數(shù)(effective-number-of-bit)計算等。

此外,您還應該充分利用FPGA提供的資源,尤其是賽靈思System Monitor和XADC,非常有利于監(jiān)控芯片上的電壓軌,進而還能有助于驗證在設(shè)計階段所執(zhí)行的電源完整性分析。此外,上述技術(shù)還能方便地報告芯片溫度,這對環(huán)境測試以及芯片溫度的功耗關(guān)聯(lián)等都有幫助。

多數(shù)情況下,簡化RTL設(shè)計并采用FPGA提供的資源對精確定位未按預期工作的區(qū)域都有極大的幫助。

遇到問題怎么辦?

在一步步推進測試計劃的過程中,您可能會遇到一兩個問題,如未能實現(xiàn)預期的功能,或在功能方面無法滿足所需的性能水平。不要擔心,我們能通過許多調(diào)查方法來確定問題根源和所需的糾正措施。

在上述情況下,不要急于馬上做出修改。首先,要重新檢查設(shè)計方案,特別是原理圖和數(shù)據(jù)手冊等設(shè)計信息。如果問題與FPGA有關(guān),則應檢查引腳約束文件是否適合設(shè)計需要,因為有可能文件與設(shè)計不同步。

如果一時找不出什么明顯錯誤,則不妨發(fā)揮一下互聯(lián)網(wǎng)的優(yōu)勢,去網(wǎng)上看看其他工程師是否也遇到過跟您同樣的問題。網(wǎng)上有很多論壇,您可在那里向其他設(shè)計人員提問。Programmable Planet和賽靈思論壇都可為基于FPGA的設(shè)計提供廣泛的支持。

說到底,硬件調(diào)試是工程設(shè)計中極富挑戰(zhàn),但又極具收獲的組成部分。若在設(shè)計早期階段即考慮到測試問題,并在設(shè)計中包含測試所需的各元素,就能顯著簡化調(diào)試工作。采用ChipScope、System Monitor和XADC等所有可用的資源來調(diào)試系統(tǒng),外加合理利用傳統(tǒng)測試設(shè)備,我們就能成功完成開發(fā)工作。

圖2:這里的優(yōu)化代碼是從連接輸出的簡單DAC接口到已知狀態(tài)的代碼片段,能夠生成Fs/2的正弦波。此類代碼的標準版可能有數(shù)百行的長度。

相關(guān)閱讀:

電磁兼容設(shè)計及測試技術(shù)分析

http://www.gdnengbo.cn/emc-art/80022187

一種實用精確的電纜測試電路設(shè)計

http://www.gdnengbo.cn/connect-art/80021760

高壓作業(yè)必備,如何做好數(shù)字隔離器的浪涌測試?

http://www.gdnengbo.cn/cp-art/80021570