【導讀】作為一個系統設計工程師,經常會遇到這個問題:是選用ASIC還是FPGA?讓我們來看一看這兩者有什么不同。在明白他們的不同后,工程師就可以知道在系統設計中的如何選擇半導體器件:ASIC,還是FPGA?

所謂ASIC,是專用集成電路(Application Specific Integrated Circuit)的簡稱,電子產品中,應用非常廣泛。ASIC的功能是固定的,它是為了專一功能而生。

FPGA取自Field Programmable Gate Array,譯為“現場(Field)可編程(Programmable)邏輯陣列(Gate Array)”。FPGA是可以反復編程的邏輯器件。簡單說,用戶可通過硬件描述語言完成的電路設計,再經綜合與布局,可產生數據流文件,最后編程下載到 FPGA 上進行測試。這個流程與ASlC在前面的流程基本一致,后面ASlC則是生成掩模,投片生產晶圓,封裝和測試,拿到專用的芯片。

采用FPGA設計,用戶不需要投片生產,就能得到合用的芯片。 FPGA與ASIC電路設計相比,周期短、風險小。所以用戶要考慮的因素主要是生產成本。在討論成本因素以前,先講一講常聽到的有關FPGA的幾個誤區:

1)“擔心產品安全性,目前主流的FPGA都是用片外的PROM或者FLASH存儲代碼,上電時從片外存儲器讀入到內部SRAM的方式,這種方式代碼很容易被拷貝。”(-轉自網上刊物)

事實上目前市場上所有使用片外存儲器讀入到內部SRAM或者使用外部CPU對器件編程的FPGA都提供編程數據流文件加密功能。以高云的GW2A家族為例,器件上提供了128位的非易失性存儲器做為用戶密鑰。編程數據流文件在由軟件工具生成的時候用戶可以選擇使用密鑰對其加密。加密算法為國際普遍使用的算法。在FPGA器件收到加密的數據流文件時會自動解密并加載到器件中。整個過程非常安全。可以想像如今在華爾街的金融機構已經用FPGA構建系統來代替大型計算機,如果沒有過硬的安全認可,是不可思議的。

高云FPGA芯片

2)“由于是采用SRAM的方式來執行邏輯,在受到強干擾,輻射等惡劣條件影響下,內部的邏輯位有可能發生一次性變更,有可能導致邏輯功能的失效,唯一恢復的辦法就是重新上電。這對于那些對安全性,可靠性有要求的應用來說尤其不利。”(-轉自網上刊物)

在特殊條件下工作的FPGA有很多種方式來應對強干擾,輻射等惡劣條件影響。而這些影響對于ASIC器件也是一樣的,只是程度上有些區別。常用的方式有采用特殊工藝如Silicon On Insulator(SOI)或者用設計方式加固SRAM單元。事實上在航空,航天等惡劣條件下工作的系統正在廣泛使用FPGA。

3)“FPGA具有相對高得多的功耗,限制了產品的應用范圍,增加了產品電源設計的難度及成本。”(-轉自網上刊物)

在近年發布的FPGA產品中有一個重要分支就是低功耗FPGA。目標市場是手機,可穿戴設備等移動設備。目前聽到多個成功應用的案例如谷歌眼鏡。總之FPGA產品多樣化。可以在規模,功能,性能,及功耗中選擇到最適合你的系統設計。

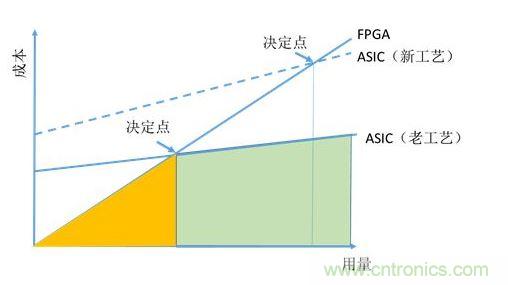

現在我們看一看成本的比較。有這樣一個誤區:“為了達到同樣的系統性能,FPGA必須選擇比ASIC更先進的工藝。這也就意味著FPGA 硅片應用成本遠高于ASIC。”讓我們看一看它們的成本有哪些。前面我們已經提到了FPGA與ASIC前面的設計流程是一樣的,我們可以簡化這個比較,認為兩者的研發成本相同。(實際上是有區別的,主要是工具價格差別很大。FPGA工具基本上都是廠家免費的,而ASIC的設計工具動輒百萬美元。)在設計完成之后,FPGA這時的成本就是器件的單個成本了。應該包括廠家晶圓,封裝和測試費用再加上毛利。ASIC這時的成本要包括一次性工程費用(英文:Non-recurring engineering,NRE)和芯片成本,應該包括廠家晶圓,封裝和測試費。我們會發現,整體成本可以用下圖來表示:

從上圖可以看出,FPGA由于沒有NRE,在用量較小的時候成本優勢明顯。由于FPGA單個芯片成本高于ASIC,所以有較大斜率。在決定點位置以后,ASIC開始有成本優勢。所以從成本因速考慮選用FPGA還是ASIC,與用量有很大關系。

上圖也顯示了半導體工藝進步的影響。芯片的密度在根據摩爾定律(Moore’s Law)增加,這是由于晶圓制造更前端的掩膜(Mask)成本成指數級上升,晶圓制造更后端的封裝成本、人力成本要么不變,要么由于芯片復雜度增加。對于一個受管腳數目限制的芯片,單個FPGA的成本已經與ASIC相同了。這樣就造成了上圖虛線所代表的新的成本線。我們可以看到“決定點”在迅速上移。這就意味著FPGA的應用空間在不斷擴大。

根據IDC的調查報告,2011年采用ASIC的設計減少至2,313項,較2002年下滑了6%。特別是在有線通訊設計領域,2011年的ASIC僅442項,明顯減少了近兩倍,并較2002年更少11%。而另一項由Altera提供的研究,一家市場研究公司估計開發一款28納米ASIC的成本約8千萬美元,而一款20納米ASIC的開發成本更高達1億600千萬美元。

高云的GW2A家族特別把降低用戶使用成本作為優先考慮。在同等密度的FPGA中提供了最多IO數。成為業界的領先者。器件采用臺積電(TSMC)的55納米工藝,邏輯單元從18K LUT到55K LUT,多達5兆位的存貯器塊能夠提供多種模式、多種深寬度配置及單雙端口的讀寫操作;多達80個18X18的DSP模塊,可進行高速的加法、減法、乘法及累積算法;498個數字單端輸入輸出,可支持從1.2V到3.3V的輸出電壓,驅動電流可配置,多種廣泛應用的輸入輸出協議如LVTTL、LVCOMS、PCI、STL、SSTL、RSDS、LVDS等;多達8個通用鎖相環工作范圍從3MHz到500MHz并提供多種用戶時鐘操作模式;動態I/O bank控制器的獨立模塊的待機工作模式以及更低的工作電壓;支持廣泛的接口標準,包括DDR2、DDR3、ADC、視頻、SPI4等。可提供多種封裝,包括:PBGA256、PBGA484、PBGA672、PBGA1156,將來可根據用戶需求,提供更多封裝類型。