【導(dǎo)讀】JESD204B是最近批準(zhǔn)的JEDEC標(biāo)準(zhǔn),用于轉(zhuǎn)換器與數(shù)字處理器件之間的串行數(shù)據(jù)接口。它是第三代標(biāo)準(zhǔn),解決了先前版本的一些缺陷。該接口的優(yōu)勢包括:數(shù)據(jù)接口路由所需電路板空間更少,建立與保持時序要求更低,以及轉(zhuǎn)換器和邏輯器件的封裝更小。多家供應(yīng)商的新型模擬/數(shù)字轉(zhuǎn)換器采用此接口,例如ADI公司的 AD9250 。

JESD204B是最近批準(zhǔn)的JEDEC標(biāo)準(zhǔn),用于轉(zhuǎn)換器與數(shù)字處理器件之間的串行數(shù)據(jù)接口。它是第三代標(biāo)準(zhǔn),解決了先前版本的一些缺陷。該接口的優(yōu)勢包括:數(shù)據(jù)接口路由所需電路板空間更少,建立與保持時序要求更低,以及轉(zhuǎn)換器和邏輯器件的封裝更小。多家供應(yīng)商的新型模擬/數(shù)字轉(zhuǎn)換器采用此接口,例如ADI公司的 AD9250 。

與現(xiàn)有接口格式和協(xié)議相比,JESD204B接口更復(fù)雜、更微妙,必須克服一些困難才能實現(xiàn)其優(yōu)勢。像任何其他標(biāo)準(zhǔn)一樣,要使該接口比單倍數(shù)據(jù)速率或雙倍數(shù)據(jù)速率CMOS/LVDS等常用接口更受歡迎,它必須能無縫地工作。雖然JESD204B標(biāo)準(zhǔn)由JEDEC制定,但某些特定信息仍需要闡明,或者可能散布于多個參考文獻(xiàn)中。另外,如果有一個簡明的指南能概要說明該標(biāo)準(zhǔn)、工作原理以及如何排除故障,無疑對使用者將極為有幫助。

本文闡釋JESD204B標(biāo)準(zhǔn)的ADC與FPGA的接口,如何判斷其是否正常工作,以及可能更重要的是,如何在有問題時排除故障。文中討論的故障排除技術(shù)可以采用常用的測試與測量設(shè)備,包括示波器和邏輯分析儀,以及Xilinx?的ChipScope或Altera?的SignalTap等軟件工具。同時闡明了接口信號傳輸,以便能夠利用一種或多種方法實現(xiàn)信號傳輸?shù)目梢暬?/p>

JESD204B概述

JESD204B標(biāo)準(zhǔn)提供一種將一個或多個數(shù)據(jù)轉(zhuǎn)換器與數(shù)字信號處理器件接口的方法(通常是ADC或DAC與FPGA接口),相比于通常的并行數(shù)據(jù)傳輸,這是一種更高速度的串行接口。該接口速度高達(dá)12.5 Gbps/通道,使用幀串行數(shù)據(jù)鏈路及嵌入式時鐘和對齊字符。它減少了器件之間的走線數(shù)量,降低了走線匹配要求,并消除了建立與保持時序約束問題,從而簡化了高速轉(zhuǎn)換器數(shù)據(jù)接口的實施。由于鏈路需要在數(shù)據(jù)傳輸之前建立,因此存在新的挑戰(zhàn),必須采用新的技術(shù)來確定接口是否正常工作,以及在接口故障時怎么辦。

JESD204B接口通過三個階段來建立同步鏈路:代碼組同步(CGS)、初始通道同步(ILAS)和數(shù)據(jù)傳輸階段。鏈路需要以下信號:共享參考時鐘(器件時鐘),至少一個差分CML物理數(shù)據(jù)電連接(稱為“通道”),以及至少一個其他同步信號(SYNC~和可能的SYSREF)。使用哪些信號取決于子類:

子類0使用器件時鐘、通道和SYNC~。

子類1使用器件時鐘、通道、SYNC~和SYSREF;

子類2使用器件時鐘、通道和SYNC~。

子類0在許多情況下足以滿足需求,因而是本文的重點。子類1和子類2提供了建立確定性延遲的方法,這在需要同步多個器件或需要系統(tǒng)同步或固定延遲的應(yīng)用中非常重要,例如一個系統(tǒng)的某個事件需要已知的采樣沿,或者某個事件必須在規(guī)定時間內(nèi)響應(yīng)輸入信號。

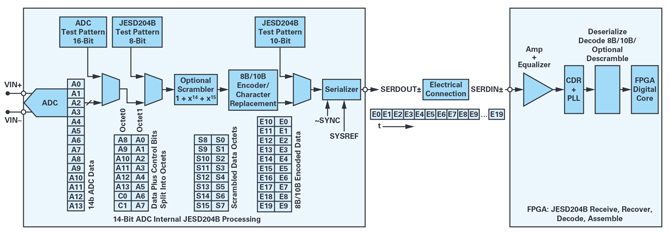

圖1顯示了從發(fā)射器件(ADC)到接收器件(FPGA)的簡化JESD204B鏈路,數(shù)據(jù)從一個ADC經(jīng)由一個通道傳輸。

雖然JESD204B規(guī)范有許多變量,但某些變量對于鏈路的建立特別重要。這些關(guān)鍵變量如下所示(注:這些值通常表示為“X ? 1”):

M:轉(zhuǎn)換器數(shù)。

L:物理通道數(shù)。

F:每幀的8位字節(jié)數(shù)。

K:每個多幀的幀數(shù)。

N和N’:分別表示轉(zhuǎn)換器分辨率和每個樣本使用的位數(shù)(4的倍數(shù))。N’的值等于N值加上控制和填充數(shù)據(jù)位數(shù)。

子類0:同步步驟

如上所述,許多應(yīng)用可以采用相對簡單的子類0工作模式,這也是建立和驗證鏈路的最簡單模式。子類0通過三個階段來建立和監(jiān)控同步:CGS階段、ILAS階段和數(shù)據(jù)階段。各階段相關(guān)的圖表以不同格式顯示數(shù)據(jù),可以在示波器、邏輯分析儀或FPGA虛擬I/O分析儀(如Xilinx ChipScope或Altera SignalTap)上觀察到這些數(shù)據(jù)。

代碼組同步(CGS)階段

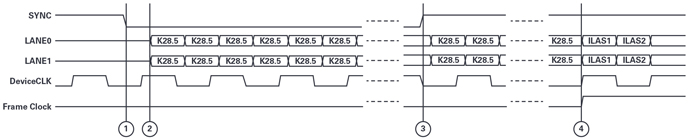

可以在鏈路上觀察到的CGS階段最重要部分如圖2所示,圖中5個突出顯示的點說明如下。

接收器通過拉低SYNC~引腳,發(fā)出一個同步請求。

收發(fā)器從下一個符號開始,發(fā)送未加擾的/K28.5/符號(每個符號10位)。

當(dāng)接收器收到至少4個無錯誤的連續(xù)/K28.5/符號時同步,然后將SYNC~引腳拉高。

接收器必須接收到至少4個無錯誤8B/10B字符,否則同步將失敗,鏈路留在CGS階段。

CGS階段結(jié)束,ILAS階段開始。

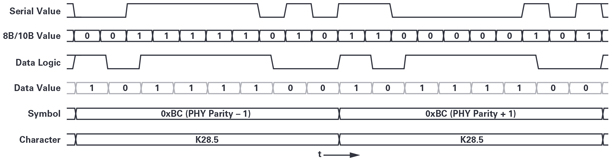

/K28.5/字符在JESD204B標(biāo)準(zhǔn)中也稱為/K/,如圖3所示。標(biāo)準(zhǔn)要求直流平衡。利用8B/10B編碼,可以實現(xiàn)平均而言包含等量1和0的平衡序列。每個8B10B字符可能具有正(1較多)或負(fù)(0較多)偏差,當(dāng)前字符的奇偶性由先前發(fā)送的字符的極性偏差決定,這通常是通過交替發(fā)送正奇偶性字與負(fù)奇偶性字來實現(xiàn)。圖中顯示了/K28.5/符號的兩種極性。

圖1.JESD204B鏈路圖:一個ADC通過一個通道與FPGA接口

圖2.JESD204B子類0鏈路信號在CGS階段的邏輯輸出(假設(shè)有兩個通道,一個器件含兩個ADC)

圖3.K28.5字符的邏輯輸出以及它如何通過JESD204B Tx信號路徑傳播

重點注意以下幾點:

串行值表示通過通道傳輸?shù)?0位的邏輯電平,可通過測量物理接口的示波器看到。

8B/10B值表示通過通道傳輸?shù)倪壿嬛担?0位),可通過測量物理接口的邏輯分析儀看到。

數(shù)據(jù)值和數(shù)據(jù)邏輯表示8B/10B編碼前JESD204B收發(fā)器模塊內(nèi)符號的邏輯電平,可通過Xilinx ChipScope或Altera SignalTap等FPGA邏輯分析工具看到。

符號表示要發(fā)送的字符的十六進(jìn)制值,注意PHY層的奇偶性。

字符表示JEDEC規(guī)范中所指的JESD204B字符。

ILAS階段

ILAS階段有4個多幀,允許接收器對齊來自所有鏈路的通道,以及驗證鏈路參數(shù)。為了調(diào)和不同長度的走線以及接收器導(dǎo)致的字符偏斜,通道必須對齊。4個多幀緊緊相連(圖4)。無論啟用加擾鏈路參數(shù)與否,ILAS始終是無加擾傳輸。

SYNC信號從低電平變?yōu)楦唠娖胶螅氵M(jìn)入ILAS階段。發(fā)送模塊內(nèi)部跟蹤到(ADC內(nèi)部)一個完整多幀后,便開始發(fā)送4個多幀。在所需的字符中插入填充數(shù)據(jù),以便傳送完整的多幀(圖4)。4個多幀包括:

多幀1:以/R/字符[K28.0]開始,以/A/字符[K28.3]結(jié)束。

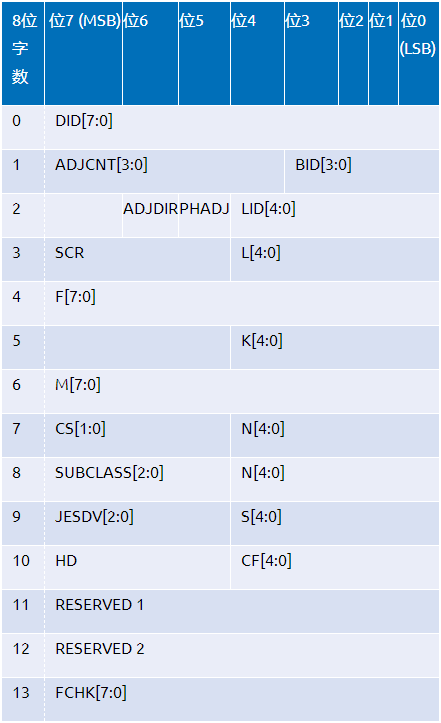

多幀2:以/R/字符開始,后接/Q/ [K28.4]字符,然后是14個配置8位字的鏈路配置參數(shù)(表1),最后以/A/字符結(jié)束。

多幀3:與多幀1相同。

多幀4:與多幀1相同。

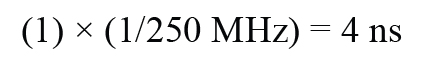

幀長度可以利用JESD204B參數(shù)計算:(S) ×(1/采樣速率)。

含義:

(樣本數(shù)/轉(zhuǎn)換器/幀)×(1/樣本速率)

示例:

采樣速率為250 MSPS、每幀每轉(zhuǎn)換器一個樣本的轉(zhuǎn)換器(注:在本例中“S”為0,因為它被編碼為二進(jìn)制值-1),其幀長度為4 ns。

(1)多幀長度可以利用JESD204B參數(shù)計算:

(2)含義:

(樣本數(shù)/轉(zhuǎn)換器/幀)×(幀數(shù)/多幀)×(1/采樣速率)

示例:

采樣速率為250 MSPS、每幀每轉(zhuǎn)換器一個樣本、每多幀有32幀的轉(zhuǎn)換器,其多幀長度為128 ns。

(3)數(shù)據(jù)階段(使能字符替換)

在數(shù)據(jù)傳輸階段,通過控制字符監(jiān)控幀對齊。在幀的結(jié)尾處執(zhí)行字符替換。在數(shù)據(jù)階段,數(shù)據(jù)或幀對齊不會造成額外開銷。字符替換允許在幀邊界處發(fā)送對齊字符,唯一條件是當(dāng)前幀的最后一個字符可以替換為上一幀的最后一個字符。這有利于(間或)確認(rèn)自ILAS序列后,對齊未改變。

出現(xiàn)下列情況時,會對發(fā)送器執(zhí)行字符替換:

若禁用了加擾,幀或多幀的最后一個8位字等于上一幀的8位字。

若使能了加擾,多幀的最后一個8位字等于0x7C,或幀的最后一個8位字等于0xFC。

發(fā)射器和接收器各自保持一個本地多幀計數(shù)器(LMFC),它持續(xù)計數(shù)到(F × K) ? 1,然后繞回到“0”重新開始計數(shù)(忽略內(nèi)部字寬)。向所有發(fā)送器和接收器發(fā)送一個公共(源)SYSREF,這些器件利用SYSREF復(fù)位其LMFC,這樣所有LMFC應(yīng)互相同步(在一個時鐘周期內(nèi))。

釋放SYNC(所有器件都會看到)后,發(fā)送器在下一次(Tx) LMFC繞回0時開始ILAS。如果F × K設(shè)置適當(dāng),大于(發(fā)送器編碼時間)+(線路傳播時間)+(接收器解碼時間),則接收數(shù)據(jù)將在下一個LMFC之前從接收器的SERDES傳播出去。接收器將把數(shù)據(jù)送入FIFO,然后在下一個(Rx) LMFC邊界開始輸出數(shù)據(jù)。發(fā)射器的SERDES輸入和接收器FIFO輸出之間的這種已知關(guān)系稱為確定性延遲。

圖4.JESD204B 子類0鏈路信號在ILAS階段的邏輯輸出

圖5./K/字符[K28.5]、/R/字符[K28.0]、/A/字符[K28.3]和/Q/字符[K28.4]圖

表1.ILAS多幀2的CONFIG表(14個JESD204B配置參數(shù)8位字)

哪些方面會出錯?

JESD204B可以說是一個復(fù)雜的接口標(biāo)準(zhǔn),操作上有許多微妙之處。要找出不能正常工作的原因,需要對可能的情形有良好的了解:

陷入CGS模式:如果SYNC保持邏輯低電平;或者脈沖高電平持續(xù)時間少于4個多幀:

檢查電路板,不上電:

SYSREF和SYNC~信號應(yīng)直流耦合。

在電路板未上電的情況下,檢查從SYNC~源(通常來自FPGA或DAC)到SYNC~輸入(通常是ADC或FPGA)的電路板SYNC~連接是否良好且具有低阻抗。

確保下拉或上拉電阻不是信號傳輸?shù)闹鲗?dǎo)因素,例如:值太小或短路就會導(dǎo)致無法正確驅(qū)動。

確認(rèn)JESD204B鏈路的差分對走線(及電纜,若使用)匹配。

確認(rèn)走線的差分阻抗為100 Ω。

檢查電路板,上電:

如果SYNC路徑中有一個緩沖器/轉(zhuǎn)換器,確保它正常工作。

確認(rèn)SYNC~源和板上電路(SYNC+和SYNC-,若為差分)配置正確,產(chǎn)生符合SYNC~接收器件要求的邏輯電平。如果邏輯電平不兼容,應(yīng)檢查源和接收配置以找出問題,否則,請咨詢器件制造商。

確認(rèn)JESD204B串行發(fā)送器和板電路配置正確,產(chǎn)生符合JESD204B串行數(shù)據(jù)接收器要求的正確邏輯電平。如果邏輯電平不兼容,應(yīng)檢查電路的來源和接收配置以找出問題。否則,請咨詢器件制造商。

檢查SYNC~信號:

如果SYNC~為靜態(tài)邏輯電平,鏈路將停留在CGS階段。可能是所發(fā)送的數(shù)據(jù)有問題,或者JESD204B接收器未對樣本進(jìn)行正確解碼。確認(rèn)發(fā)送的是/K/字符,確認(rèn)接收配置設(shè)置,確認(rèn)SYNC~源,檢查板電路,考慮過驅(qū)SYNC~信號并強迫鏈路進(jìn)入ILAS模式,從而找出鏈路接收器和收發(fā)器問題。否則,請咨詢器件制造商。

如果SYNC~為靜態(tài)邏輯高電平,確認(rèn)源器件是否正確配置了SYNC~邏輯電平。檢查上拉和下拉電阻。

如果SYNC~脈沖變?yōu)楦唠娖剑缓蠓祷剡壿嫷碗娖綘顟B(tài)且持續(xù)時間少于6個多幀周期,則JESD204B鏈路會從CGS階段前進(jìn)到ILAS階段,但會停留在后一階段。這可能意味著/K/字符正確,CDR的基本功能正常。請參閱“ILAS故障排除”部分。

如果SYNC~變?yōu)楦唠娖角页掷m(xù)時間大于6個多幀周期,則鏈路會從ILAS階段前進(jìn)到數(shù)據(jù)階段,但會在后一階段發(fā)生故障;相關(guān)故障排除提示請參閱“數(shù)據(jù)階段”部分。

檢查串行數(shù)據(jù)

確認(rèn)收發(fā)器的數(shù)據(jù)速度和接收器的預(yù)期速率是否相同。

用高阻抗探頭(如果可能,使用差分探頭)測量通道;如果字符看起來錯誤,確保通道差分走線匹配,PCB上的返回路徑未中斷,并且器件正確焊接到PCA上。與ILAS和數(shù)據(jù)階段的(看似)隨機字符不同,CGS字符很容易在示波器上識別(如果使用速度足夠高的示波器)。

用高阻抗探頭驗證/K/字符。

■如果/K/字符正確,則表示鏈路的收發(fā)器端工作正常。

■如果/K/字符不正確,則表示收發(fā)器器件或電路板通道信號有問題。

若是直流耦合,確認(rèn)發(fā)送器和接收器共模電壓在器件的要求范圍內(nèi)。

■根據(jù)實施情況,發(fā)射器共模電壓范圍可能為490 mV至1135 mV。

■根據(jù)實施情況,接收器共模電壓范圍可能為490 mV至1300 mV。

確認(rèn)數(shù)據(jù)通道上的發(fā)射器CML差分電壓(注意,CML差分電壓等于信號各側(cè)電壓擺幅的兩倍)。

■對于3.125 Gbps及以下的速度,發(fā)射器CML差分電壓范圍為0.5 V p-p至1.0 V p-p。

■對于6.374 Gbps及以下的速度,發(fā)射器CML差分電壓范圍為0.4 V p-p至0.75 V p-p。

■對于12.5 Gbps及以下的速度,發(fā)射器CML差分電壓范圍為0.360 V p-p至0.770 V p-p。

確認(rèn)數(shù)據(jù)通道上的接收器CML差分電壓(注意,CML差分電壓等于信號各側(cè)電壓擺幅的兩倍)。

■對于3.125 Gbps及以下的速度,接收器CML差分電壓范圍為0.175 V p-p至1.0 V p-p。

■對于6.374 Gbps及以下的速度,接收器CML差分電壓范圍為0.125 V p-p至0.75 V p-p。

■對于12.5 Gbps及以下的速度,接收器CML差分電壓范圍為0.110 V p-p至1.05 V p-p。

如果存在預(yù)加重選項,應(yīng)啟用該選項并觀察數(shù)據(jù)路徑上的數(shù)據(jù)信號。

確認(rèn)發(fā)射器與接收器的M和L值一致,否則數(shù)據(jù)速率可能不匹配。例如,M=2且L=2這種情況的預(yù)期串行接口數(shù)據(jù)速率是M=2且L=1這種情況的一半。

確保進(jìn)入發(fā)射器和接收器的器件時鐘已鎖相且頻率正確。

如果SYNC變?yōu)楦唠娖角页掷m(xù)約4個多幀,則停留在ILAS模式:

鏈路參數(shù)沖突

■確認(rèn)鏈路參數(shù)未偏移1(許多參數(shù)規(guī)定為值減1)。

■確認(rèn)ILAS多幀傳送正確,確認(rèn)收發(fā)器件、接收器件和ILAS第二多幀傳送的鏈路參數(shù)正確。

■計算預(yù)期ILAS長度(tframe, tmultiframe, 4 × tmultiframe),確認(rèn)ILAS已嘗試大約4個多幀。

確認(rèn)所有通道工作正常。確保不存在多通道/多鏈路沖突。

進(jìn)入數(shù)據(jù)階段但鏈路偶爾會復(fù)位(先返回CGS和ILAS階段,再進(jìn)入數(shù)據(jù)階段):

周期性或帶隙周期性SYSREF或SYNC~信號的建立和保持時間無效。

鏈路參數(shù)沖突。

字符替換沖突。

加擾問題(如果啟用)。

通道數(shù)據(jù)損壞、噪聲或抖動可能迫使眼圖閉合。

雜散時鐘或器件時鐘的抖動過大

關(guān)于排除鏈路故障的其他一般提示:

以允許的最低速度運行轉(zhuǎn)換器和鏈路,這樣就可以使用較容易獲得的低帶寬測量儀器。

設(shè)置允許的最少M、L、K、S組合

可能時使用測試模式

使用子類0來排除故障

排除故障時禁用加擾

本故障排除指南并未窮盡所有可能,但為使用JESD204B鏈路以及希望了解更多信息的工程師提供了一個很好的基本框架。

以上是JESD204B規(guī)范的概述,并提供了鏈路相關(guān)的實用信息。希望涉及到這一最新高性能接口標(biāo)準(zhǔn)的工程師能從中獲益,并對排除故障有所幫助。

(來源:ADI公司,Anthony Desimone,高速轉(zhuǎn)換器部門的應(yīng)用工程師;Michael Giancioppo,應(yīng)用工程師)

免責(zé)聲明:本文為轉(zhuǎn)載文章,轉(zhuǎn)載此文目的在于傳遞更多信息,版權(quán)歸原作者所有。本文所用視頻、圖片、文字如涉及作品版權(quán)問題,請電話或者郵箱editor@52solution.com聯(lián)系小編進(jìn)行侵刪。

推薦閱讀:

2021 年 Digi-Key Electronics 新增了 500 多家供應(yīng)商和 125,000 多個 SKU

雙極結(jié)型晶體管——MOSFET的挑戰(zhàn)者

Digi-Key 與 CalcuQuote 合作,提供報價 API 集成支持,為客戶提供一種更簡便的途徑來實現(xiàn) 30 天定價保證