【導讀】本文研究了一種可行的、簡單實用及高精度的電容在線測試電路。隨著EDA技術的快速發展,FPGA以其高集成度、高可靠性及靈活性等特點正在快速成為數字系統開發平臺,在多種領域都有非常廣闊的應用前景。本設計結合上述兩特點,設計了一種基于向FPGA內植入Nios II嵌入式軟核作為控制器的電容在線測試電路。

1、測試原理

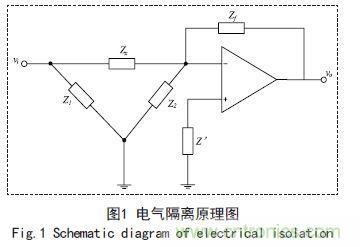

在線測試的基本思想是應用電氣隔離技術,將被測元器件在電氣上和與其相連的元件隔離,進而一一檢測PCB板上的每一個元件。隔離方法如圖1所示。

設待測元件為Zx,周圍與之相連的元件阻抗等效為Z1、Z2,并將其另一端與測試電路同地。因為運放正向輸入端接地,根據“虛地”原則,Z2兩端等電位,都為地,即Z2被隔離;另外Vi為理想電壓源時,內阻為零,Z1可視為電壓源的輸出負載,不影響Zx上電壓降,即Z1也被隔離。即:

可見,只要確定輸入,測得輸出結果,就可計算出被測元件的大小。

2、電容測試電路的硬件設計

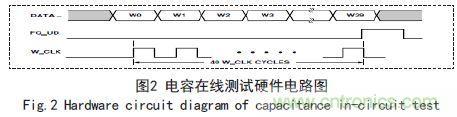

電容在線測試的硬件電路如圖2所示。

R2、C1和U1共同構成一個反向積分器,為減少運放振蕩的可能性,所以采用反向輸入。R1的作用是使有內部相位補償的運放開環特性與積分電路的頻率特性相同,保證一定頻率范圍內開環增益與頻率無關。Header2為被測電容的接入插槽。Z1、Z2是與被測電容相連的干擾阻抗。被測電容同U2和R8-11一起構成微分電路。小阻值R3起限制輸入電流的作用,亦即限制了R8-11中的電流。小容量C2起相位補償作用,提高電路的穩定性。另外,在器件的選擇上,運放選用LM318,對于C1和C2,應選用絕緣電阻大的薄膜電容,不宜用鋁電容或鉭電容,本設計選用的是聚丙烯電容。

當Vi為一正弦信號時,積分器的輸出為:

可見,在正弦信號的激勵下,R8-11選擇合適,就能得到正比于被測電容Cx的輸出電壓Vv_out,繼而可以算出被測電容值。

[page]

3、信號源電路

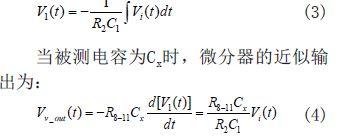

電容測試需要在測試電路輸入端加交流信號,并且要求頻率可調。本文采用DDS專用芯片AD9850進行交流信號源的設計。AD9850內部有40位控制字,其中32位用于頻率控制,5位用于相位控制,1位用于電源休眠控制,2位用于選擇工作方式。這40位控制字可以通過并行或串行方式接入到控制器FPGA,本文采用串行裝載控制字,以節約I/O口,圖3為控制字的串行加載時序圖。

串行輸入方式,在W_CLK上升沿把數據位D7的一位數據串行輸入,當輸入40位后,用一個FQ_UD脈沖即可更新輸出頻率和相位。圖4為DDS硬件電路圖。

其中,D0~D7為八位數據輸入端口,給內部寄存器裝入40位控制數據,本文采用串行輸入,所以只用到D7位與FPGA相連;CLKIN為外部參考時鐘輸入,本設計采用100M外部時鐘輸入;W_CLK為字輸入信號,上升沿有效;FQ_UD為頻率更新控制信號,時鐘上升沿確認輸入數據有效;VINP和VINN分別為內部比較器的正負輸入端;IOUT為內部DAC輸出端;IOUTB為“互補”DAC輸出端;AVDD和DVDD采用+5V供電。IOUT輸出信號經過濾波器后作為測試電路的激勵信號。

其中,D0~D7為八位數據輸入端口,給內部寄存器裝入40位控制數據,本文采用串行輸入,所以只用到D7位與FPGA相連;CLKIN為外部參考時鐘輸入,本設計采用100M外部時鐘輸入;W_CLK為字輸入信號,上升沿有效;FQ_UD為頻率更新控制信號,時鐘上升沿確認輸入數據有效;VINP和VINN分別為內部比較器的正負輸入端;IOUT為內部DAC輸出端;IOUTB為“互補”DAC輸出端;AVDD和DVDD采用+5V供電。IOUT輸出信號經過濾波器后作為測試電路的激勵信號。

結果中表示數據不停變化或者結果超出量程。

通過上述實測值與標準值的比較可以看出本文設計的由FPGA控制的電容在線測試系統具有多量程自動選擇,測試精度高,使用方便等特點,測試范圍達到0.01μF~3μF.經理論分析和試驗證明,該設計具有很強的實用性和可靠性。

相關閱讀:

設計分享:采用上位機與FPGA開發板的光纖通道接口適配器設計

FPGA研發之道——靈活性的陷阱

淺析FLASH和反熔絲技術為基礎的FPGA