許多信號(hào)處理應(yīng)用都需要進(jìn)行上采樣。從概念上講,對(duì)數(shù)據(jù)向量進(jìn)行M倍上采樣的最簡(jiǎn)單方法是用實(shí)際頻率分量數(shù)的(M-1)倍個(gè)零填充數(shù)據(jù)向量的離散傅里葉變換(DFT),然后將零填充向量轉(zhuǎn)換回時(shí)域。但這種方法計(jì)算量很大,因此不能在FPGA內(nèi)部高效實(shí)現(xiàn)。在本文介紹的高效并行實(shí)時(shí)上采樣電路中,每個(gè)ADC時(shí)鐘可產(chǎn)生M個(gè)上采樣值,其中M是所需的上采樣倍數(shù)。在我們的Virtex-6 XC6VLX75T FPGA實(shí)現(xiàn)方案中,上采樣倍數(shù)M為4,可以作為較普遍方法的一個(gè)實(shí)例。

我們并行上采樣方法的總體概念源于某些作者所稱的“窗口SINC插值”,這種方法在文獻(xiàn)資料中有一些非常精彩的專文介紹。

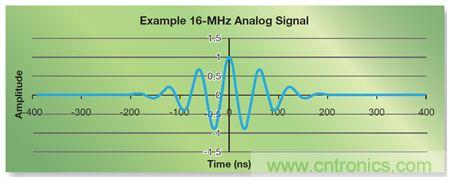

為了更好的說明,現(xiàn)以圖1中所示的16MHz模擬信號(hào)為例。該信號(hào)的表達(dá)式為:

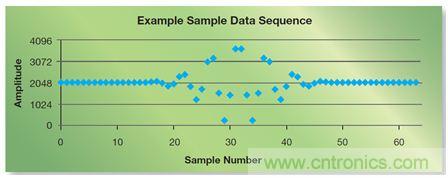

如果用12位ADC以80MHz的頻率對(duì)圖1所示的信號(hào)進(jìn)行采樣或量化,輸入范圍為ADC完整輸入范圍的97.7%,則每個(gè)信號(hào)周期只能采樣五次,產(chǎn)生的樣本數(shù)據(jù)序列如圖2所示。如果對(duì)該示例數(shù)據(jù)序列進(jìn)行四倍上采樣,則有效采樣率為320MHz,每個(gè)信號(hào)周期能夠提供20個(gè)樣本。雖然您可以使用本文介紹的方法進(jìn)行更高倍數(shù)的上采樣,但為了說明起見我們還是使用M=4的上采樣。

當(dāng)然,還可以通過直接在ADC生成的數(shù)據(jù)序列的每個(gè)實(shí)際樣本值之間插入(M-1)個(gè)零來獲得上采樣數(shù)據(jù)向量及所需的樣本數(shù)(公認(rèn)效果較差)。該“零插入步驟”對(duì)應(yīng)于復(fù)制頻域中的原始信號(hào)頻譜。通過對(duì)得到的“零填充”時(shí)域信號(hào)進(jìn)行低通濾波,就能去除頻域中所需頻譜的“復(fù)本”,從而獲得上采樣數(shù)據(jù)向量。

FIR濾波器設(shè)計(jì)

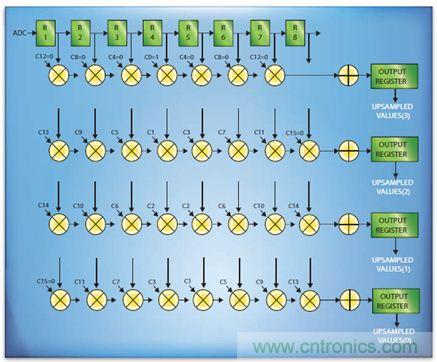

頻域中的理想(磚墻式)低通濾波器相當(dāng)于在時(shí)域中用無限域Sinc函數(shù)作卷積。因此為近似化所需的卷積運(yùn)算,可讓前述的零填充時(shí)域信號(hào)通過速率為ADC時(shí)鐘頻率M倍的對(duì)稱低通FIR濾波器,該濾波器拓?fù)浣Y(jié)構(gòu)與圖3所示的示例31抽頭FIR濾波器相同。用這種方法,我們可以實(shí)時(shí)生成上采樣數(shù)據(jù)向量。圖3中的R1、R2、...、R31代表速率為ADC時(shí)鐘頻率M倍的寄存器,C0、C1、…、C15代表FIR濾波器的系數(shù)。

需要說明的是,圖3所示的FIR濾波器中的大部分寄存器在任何特定時(shí)鐘間隔內(nèi)都會(huì)包含0,而非實(shí)際的樣本數(shù)據(jù)。以M=4為例,當(dāng)R1包含實(shí)際樣本數(shù)據(jù)時(shí),R2、R3和R4將包含0。當(dāng)R1包含實(shí)際樣本數(shù)據(jù)時(shí),R5、R9、R13、R17、R21、R25和R29也將包含實(shí)際樣本數(shù)據(jù),其余的寄存器將包含0。在下一時(shí)鐘間隔中,R2、R6、R10、R14、R18、R22、R26和R30將包含實(shí)際樣本數(shù)據(jù)。

[page]

如圖3所示,由于在通過FIR濾波器的每M個(gè)樣本中有M-1個(gè)樣本為0,就M=4、使用31抽頭FIR濾波器的情況而言(如圖4所示),您可以將濾波器分解開,并行產(chǎn)生M個(gè)輸出。采用這種實(shí)現(xiàn)方案,并行FIR濾波器的工作頻率為ADC的基本時(shí)鐘頻率,而非ADC時(shí)鐘頻率的M倍。

如圖4所示,您可以設(shè)定窗口SINC函數(shù)的系數(shù)Cw(n)來最大限度地減少實(shí)現(xiàn)該FIR濾波器所需的乘法器數(shù)量。對(duì)于T個(gè)抽頭的低通FIR濾波器而言,可通過下式得出最佳系數(shù):

這里的漢寧窗系數(shù)的計(jì)算方法為:

窗口SINC函數(shù)系數(shù)Cw(n)隨即通過對(duì)應(yīng)的C(n)和H(n)值相乘即可得到,如:

在M=4時(shí),如果按上面介紹的方法計(jì)算31抽頭FIR濾波器的系數(shù),令C0=1.0,C4=C8=C12=C15=0,則無需使用與圖4中這些系數(shù)有關(guān)的9個(gè)乘法器。此外,由于生成UPSAMPLED VALUE(1)每個(gè)系數(shù)會(huì)使用兩次,用戶可以“折疊”該實(shí)現(xiàn)方案,比如在相乘之前讓R1和R8相加,這樣就可以去掉四個(gè)乘法器。最后得到的設(shè)計(jì)僅使用18個(gè)乘法器每時(shí)鐘周期就可產(chǎn)生四個(gè)上采樣值。需要注意的是按上文介紹的設(shè)計(jì)方法,每個(gè)原始樣本值會(huì)原樣從并聯(lián)濾波器輸出。

該VHDL實(shí)現(xiàn)方案假定樣本數(shù)據(jù)為12位,即可能來自美國模擬器件公司的AD9670八通道超聲前端集成電路的數(shù)據(jù)。濾波器系數(shù)表達(dá)為25位定點(diǎn)常數(shù),以與集成到FPGA芯片上的乘法器輸入位數(shù)相匹配。來自ADC的輸入樣本先饋入與輸入引腳相連的寄存器(圖4中的R1),上采樣輸出值則使用與輸出引腳相連的寄存器。寄存器R2到R8屬芯片內(nèi)部寄存器。寄存器R1到R8故意設(shè)定為15位寬度,以便為綜合后邏輯提供執(zhí)行計(jì)算所需的動(dòng)態(tài)余量。該設(shè)計(jì)能檢查溢出或下溢,還能將結(jié)果鉗制在有效范圍以內(nèi)。

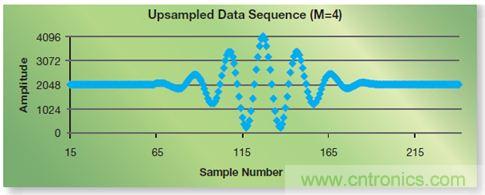

無需流水線化

圖5顯示的是使用免費(fèi)的WebPACK工具中提供的14.7版ISim仿真器對(duì)該VHDL模型進(jìn)行仿真并將饋送圖2中的采樣/量化12位數(shù)據(jù)序列后得到的上采樣數(shù)據(jù)序列。每個(gè)原始的12位樣本均保持不變,原因上文已述。原始波形中每個(gè)實(shí)際樣本之間插入了三個(gè)新樣本。

計(jì)算所得(上采樣所得)值與原始模擬信號(hào)中理想值之間最大的誤差為整個(gè)范圍的0.464%,平均誤差為整個(gè)范圍的0.070%。當(dāng)然因初始量化步驟原因,在采樣/量化12位源矢量數(shù)據(jù)值中存在1/2 LSB的誤差(合整個(gè)范圍的0.012%)。

布局布線設(shè)計(jì)使用19個(gè)DSP48E1模塊,但占用的Virtex-6 Slice資源不足1%,無需流水線化即可運(yùn)行在107MHz下。

我們使用WebPACK工具14.7版在XC6VLX75T-3FF484 Virtex-6 FPGA上實(shí)現(xiàn)這一上采樣器。布局布線設(shè)計(jì)占用該器件中288個(gè)DSP48E1模塊中的19個(gè),但使用的Slice資源不足1%。最終得到的上采樣電路能夠運(yùn)行在107MHz下。無需讓濾波器流水線化即可實(shí)現(xiàn)這一性能。此外,我們還開發(fā)出了用流水線實(shí)現(xiàn)的版本,可以工作在217MHz以上。

雖然XC6VLX75T-3FF484是Virtex-6系列中的最低端成員,但芯片上仍集成有288個(gè)帶有25x18位乘法器的DSP48E1模塊。換言之,在理論上足以實(shí)現(xiàn)15個(gè)圖4所示的并行上采樣FIR濾波器。我們制作的原型環(huán)形陣列超聲系統(tǒng)使用了八套以80MHz的頻率運(yùn)行在XC6VLX75T FPGA上的上采樣器,在波束成形之前對(duì)來自八通道Analog Devices AD9670超聲前端芯片的數(shù)據(jù)進(jìn)行上采樣處理。在該系統(tǒng)中,上采樣器按仿真預(yù)測(cè)的方式運(yùn)行,在以AD9670 ADC的基本時(shí)鐘頻率80MHz運(yùn)行的情況下,能使用上采樣到320MHz的數(shù)據(jù)實(shí)時(shí)完成波束成形。

最大型Virtex-6 FPGA器件XC6VSX475T包含有2,016個(gè)25x18位乘法器,在理論上一個(gè)芯片就可以實(shí)現(xiàn)106個(gè)圖4所示類型的上采樣濾波器。

只要濾波器使用本文介紹的高效并行拓?fù)浣Y(jié)構(gòu)進(jìn)行設(shè)計(jì),就能夠使用實(shí)現(xiàn)在工作頻率為107MHz的XC6VLX75T-3FF484 FPGA上的FIR濾波器完成M=4倍的實(shí)時(shí)上采樣。原始數(shù)據(jù)樣本將原封不動(dòng)通過濾波器,并行產(chǎn)生(M-1)=3個(gè)上采樣值。這種簡(jiǎn)明的FIR濾波器設(shè)計(jì)方法無需借助復(fù)雜精密的濾波器設(shè)計(jì)工具就能提供優(yōu)異的結(jié)果。本文介紹的思路稍加拓展,就可以使用更大的因數(shù)進(jìn)行上采樣,或者是使用抽頭數(shù)更多的FIR濾波器降低計(jì)算出的上采樣值的誤差。

這種簡(jiǎn)明的FIR濾波器設(shè)計(jì)方法無需借助復(fù)雜精密的濾波器設(shè)計(jì)工具就能提供優(yōu)異的結(jié)果。

相關(guān)閱讀:

菜鳥升級(jí)必備:通透了解FPGA設(shè)計(jì)流程

工程師入門首選:FPGA學(xué)習(xí)中必須注意的要點(diǎn)

如果FPGA設(shè)計(jì)中出現(xiàn)時(shí)序違規(guī),要怎么辦?