【導讀】可編程邏輯器件(PLD)是一種“與-或”兩級式結構器件,除了具有高速度、高集成度性能之外,其最大的特點就是用戶可定義其邏輯功能。因此PLD能夠適應各種需求,大大簡化系統設計,縮小系統規模,提高系統可靠性,受到廣大工程技術人員的青睞。

可編程邏輯器件種類繁多,性能各異,主要有以下幾種基本類型:可編程只讀存儲器(PROM),現場可編程邏輯陣列(FPLA),編程陣列邏輯(PAL),通用陣列邏輯(GAL)。通用陣列邏輯GAL(Generic ArrayLogic)是新一代的可編程邏輯器件,是采用先進的E2CMOS工藝制造的大規模集成電路,是新產品設計的理想器件。用戶可將設計的邏輯電路通過IBM-PC機對GAL芯片編程。編程過程可分為三步:(1)根據設計要求寫出與或邏輯表達式的布爾方程;(2)利用編譯器,由計算機輔助編程,得到陣列的熔絲圖,并驗證其正確性;(3)由于GAL的立即電可擦性,把編譯器的輸出送入編程器。編程器便按已確定的熔絲圖將新的內部結構信息存儲起來。這種編程方法簡單易行。

系統組成與系統設計

系統的組成

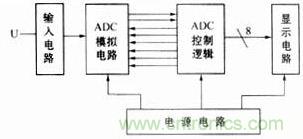

我們介紹的系統是一種基于兩次采樣的高準確度A/D轉換器。它的計數容量可達兩百萬碼,相當于六位半的A/D轉換器,是目前國內所能做到的一種較高準確度的A/D轉換器。它的工作原理是對被測信號進行兩次采樣:第一次采樣由雙積分型A/D轉換器把被測信號高位轉換成對應的數字量N2h。第二次采樣的定時積分時間要比第一次采樣的定時積分時間延長m倍,并用N2h來定時接通相應的基準電壓到求和積分器。定值積分時則改用小基準電壓Es/n來進行放電,從而獲得與被測信號低位相應的讀數N2l。綜合兩次采樣結果,A/D轉換器的總計數值為:mnN2h+N2l。它的總體框圖如圖1所示。

圖1:A/D轉換器總體框圖

由于系統正常工作時需要一個龐大的邏輯控制電路來完成兩次采樣過程,所以我們采用PLD來實現硬件控制邏輯。

系統的設計

在所有PLD中,由于GAL器件具有低功耗、高速度、可重復編程和輸出可重組態的特點,加上它的性價比明顯優于SSI/MSI器件,所以被選用來完成高準確度A/D轉換器的硬件邏輯控制電路。

硬件邏輯控制電路

GAL16V8芯片主要有五種輸出配置功能。設計中采用了其寄存器型器件中的組合輸出結構和寄存器型輸出結構。我們采用的GAL16V8芯片如圖2所示。

圖2:GAL芯片圖

它的各個管腳定義如下:

mT1:定時積分的定時時間信號(低電平有效),Th:反饋定時信號(低電平有效),ST:ADC轉換啟動信號(正跳沿有效),Sc:二次采樣信號(高電平有效),INPUT:檢零信號輸入(Ux>0時為0,Ux<0時為1),Tx:結果計數輸出(高電平有效),Sg:極性輸出(Ux>0時為0,Ux<0時為1),INT1:中斷信號(正跳沿有效),Kc:放電回路控制(高電平有效),Kx:被測量接入控制(高電平有效),VrN:負基準接入控制(高電平有效),Vr:正基準接入控制(高電平有效),Vr-10:十分之一正基準(高電平有效),Csg:釋放極性輸出寄存器(高電平有效),CLK:時鐘輸入端。

硬件邏輯控制電路工作過程

硬件邏輯電路工作時,A/D轉換啟動信號ST由“0”變“1”,標志第一次采樣正式開始。同時,Kx變為高電平,表示接入被測量Ux;mT1變為低電平,系統進入第一次采樣的定時積分時間。假設Ux>0,則檢零信號INPUT為“0”。當mT1變為高電平時,第一次采樣的定時積分時間結束。接入VrN,進入第一次采樣的定量積分階段。當檢零信號發生變化時,表明定量積分結束。在定量積分過程中,Tx有計數結果輸出,這是被測信號的高位值。中斷信號INT1由“1”變“0”,表示第一次采樣結束,系統進入休止階段。當ST和二次采樣信號Sc同時產生正跳沿時,系統進入第二次采樣階段。在第二次采樣過程中,邏輯控制過程與第一次采樣大致相同,只是定時積分時間變為第一次采樣定時積分時間的m倍,即mT1,而且在每一個T1時間內,都接通反饋定時信號Th。在定值積分階段,改用小基準電壓Vr-10來進行放電。從而Tx有計數結果輸出,這是被測信號的低位值。至此,兩次采樣A/D轉換結束。

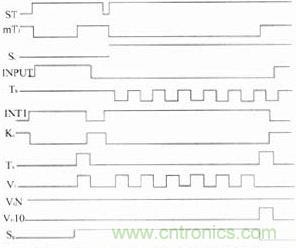

硬件邏輯控制電路時序圖

利用可編程邏輯器件設計控制電路的關鍵在于正確畫出邏輯電路的時序圖。通過準確分析兩次采樣A/D轉換器的邏輯電路,畫出它的時序圖。

(1)被測電壓為正時,GAL各管腳的時序圖如圖3所示。

圖3:U大于0時的硬件邏輯控制時序圖

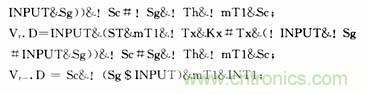

(2)被測電壓為負時,GAL各管腳的時序圖如圖4所示。

圖4:U小于0時的硬件邏輯控制時序圖

GAL可編程器件程序

根據硬件邏輯電路時序圖,現對GAL16V8芯片進行編程,完成上述邏輯功能。程序如下:

通過示波器對GAL16V8芯片各管腳輸出的波形進行觀察,得到正確的波形輸出。把采用GAL后測得的數據與原有的邏輯電路測得的數據進行比較,證明利用GAL所得的數據完全正確。因此,由GAL設計高準確度A/D轉換器的硬件邏輯控制電路是可行的。此外,由于GAL只有一個時鐘控制端,在信號進行動作時,為減少由于時鐘引起的誤差,使用的時鐘頻率要高于計數器使用時鐘頻率的兩倍以上。時鐘頻率越高,所帶來的誤差就越小。

與一般邏輯電路相比,GAL不僅保證了系統的正確性,更提高了系統的保密性和可靠性。